正确理(lǐ)解AC耦合電容

在高(gāo)頻(pín)電路設計中,經常會用(yòng)到AC耦合電容,要麽在芯片之間加兩顆直連,要麽在芯片與連接器之間加兩顆。看似簡單,但一切都因爲信号的(de)高(gāo)速而不同。信号的(de)高(gāo)速傳輸使這(zhè)顆電容變得(de)不“理(lǐ)想”,這(zhè)顆電容沒有設計好,就可(kě)能會導緻整個(gè)項目的(de)失敗。因此,對(duì)高(gāo)速電路而言,這(zhè)顆AC耦合電容沒有優化(huà)好将是“緻命”的(de)。

下(xià)面筆者依據之前的(de)項目經驗,盤點分(fēn)析一下(xià)我在這(zhè)顆電容的(de)使用(yòng)上遇到的(de)一些問題。

最開始要先明(míng)白AC耦合電容的(de)作用(yòng)。一般來(lái)講,我們用(yòng)AC耦合電容來(lái)提供直流偏壓,就是濾出信号的(de)直流分(fēn)量,使信号關于0軸對(duì)稱。既然是這(zhè)個(gè)作用(yòng),那麽這(zhè)顆電容是不是可(kě)以放在通(tōng)道的(de)任何位置呢(ne)?這(zhè)就是筆者最初做(zuò)高(gāo)頻(pín)電路時(shí),在這(zhè)顆電容使用(yòng)上遇到的(de)第一個(gè)問題——AC耦合電容到底該放在哪。

這(zhè)裏拿一個(gè)項目中常遇到的(de)典型通(tōng)路來(lái)分(fēn)析。

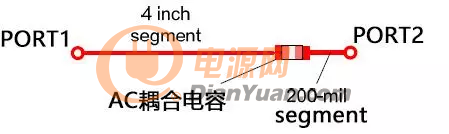

圖1:AC耦合電容典型通(tōng)路

在低速電路設計中,這(zhè)顆電容可(kě)以等效成理(lǐ)想電容。而在高(gāo)頻(pín)電路中,由于寄生電感的(de)存在以及闆材造成的(de)阻抗不連續性,實際上這(zhè)顆電容不能看作是理(lǐ)想電容。這(zhè)裏信号頻(pín)率2.5G,通(tōng)道長(cháng)度4000mil,AC耦合電容的(de)位置分(fēn)别在距離發送端和(hé)接收端200mil的(de)位置。我們看一下(xià)仿真出的(de)眼圖的(de)變化(huà)。

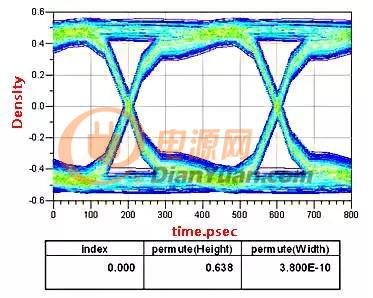

圖2:AC耦合電容靠近發送端的(de)眼圖

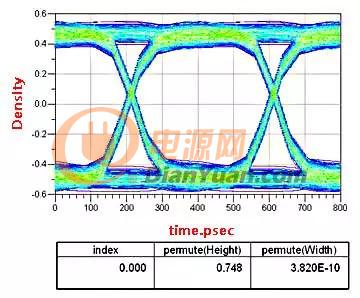

圖3:AC耦合電容靠近接收端的(de)眼圖

顯然,這(zhè)顆AC耦合電容靠近接收端的(de)時(shí)候信号的(de)完整性要好于放在發送端。我的(de)理(lǐ)解是這(zhè)樣的(de),非理(lǐ)想電容器阻抗不連續,信号經過通(tōng)道衰減後反射的(de)能量會小于直接反射的(de)能量,所以絕大(dà)多(duō)數串行鏈路要求這(zhè)顆AC耦合電容放在接收端。但也(yě)有例外,筆者之前做(zuò)闆對(duì)闆連接時(shí)遇到過這(zhè)個(gè)問題,查PCIE規範發現如果是兩個(gè)闆通(tōng)常放置在發送端上,此時(shí)還(hái)利用(yòng)到了(le)AC耦合電容的(de)另外一個(gè)作用(yòng)——過壓保護。比如說SATA,所以通(tōng)常要求靠近連接器放置。

解決了(le)放置的(de)問題,另一個(gè)困擾大(dà)家的(de)就是容值的(de)選取了(le)。這(zhè)樣說,我們的(de)整個(gè)串行鏈路等效出的(de)電阻R是固定的(de),那麽AC耦合電容C的(de)選取将會關系到時(shí)間常數(RC),RC越大(dà),過的(de)直流分(fēn)量越大(dà),直流壓降越低。既然這(zhè)樣,AC耦合電容可(kě)以無限增大(dà)嗎?顯然是不行的(de)。

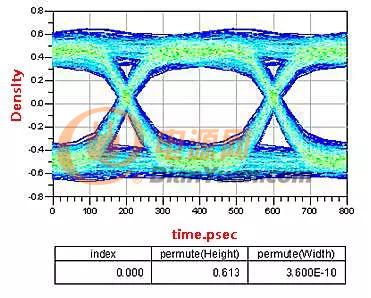

圖4:AC耦合電容增大(dà)後測量到的(de)眼圖

同樣的(de)位置,與圖3相比可(kě)以看出增大(dà)耦合電容後,眼高(gāo)變低。原因是“高(gāo)速”使電容變的(de)不理(lǐ)想。感應電感會産生串聯諧振,容值越大(dà),諧振頻(pín)率越低,AC耦合電容在低頻(pín)情況下(xià)呈感性,因此高(gāo)頻(pín)分(fēn)量衰減增大(dà),眼高(gāo)變小,上升沿變緩,相應的(de)JITTER也(yě)會增大(dà)。

通(tōng)常建議(yì)AC耦合電容在0.01uf~0.2uf之間,項目中0.1uf比較常見。推薦使用(yòng)0402的(de)封裝。

最後,解決了(le)以上兩個(gè)問題,再從PCB設計上分(fēn)析一下(xià)這(zhè)顆電容的(de)優化(huà)設計。實際在項目中,與AC耦合電容的(de)位置、容值大(dà)小這(zhè)些可(kě)見因素相比,更加難以捉摸的(de)是闆材本身(包括焊盤的(de)精度、銅箔的(de)均勻度等)以及焊盤處的(de)寄生電容對(duì)信号完整性的(de)影(yǐng)響。我們知道,高(gāo)頻(pín)信号必須沿著(zhe)有均勻特征阻抗的(de)路徑傳播,如果遇到阻抗失配或者不連續的(de)情況時(shí),部分(fēn)信号會被反射回發射端,造成信号的(de)衰減,影(yǐng)響信号的(de)完整性。項目中,這(zhè)種情況通(tōng)常會出現在焊盤或者是闆載連接器處。筆者最初涉及的(de)高(gāo)速電路設計時(shí),經常遇到這(zhè)個(gè)問題。

解決這(zhè)個(gè)問題要從兩個(gè)方面入手。首先在闆材的(de)選取上,我們在應用(yòng)中通(tōng)常選用(yòng)高(gāo)性能的(de)ROGERS闆材,羅傑斯的(de)闆材在銅箔厚度的(de)控制上非常精确,均勻的(de)銅箔覆蓋大(dà)大(dà)降低了(le)阻抗的(de)不連續性;然後在消除焊盤處的(de)寄生電容上,業内常見的(de)辦法是在焊盤處做(zuò)隔層處理(lǐ)(挖空位于焊盤正下(xià)方的(de)參考平面區(qū)域,在内層創建銅填充),通(tōng)過增大(dà)焊盤與其參考平面(或者是返回路徑)之間的(de)距離,減小電容的(de)不連續性。在筆者的(de)項目中多(duō)采用(yòng)介質均勻、銅箔寬度控制精确的(de)ROGERS闆材也(yě)有效提高(gāo)了(le)焊盤的(de)加工精度。

通(tōng)過仿真對(duì)比一下(xià)ROGERS闆材做(zuò)精确隔層處理(lǐ)前後的(de)信号完整性。

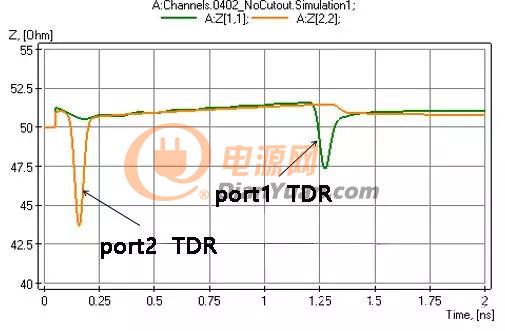

圖5:做(zuò)隔層處理(lǐ)前的(de)TDR